Расчёт оптимальных параметров настройки И регулятора

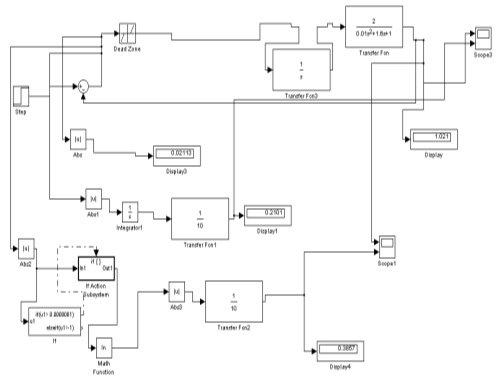

Схема И регулятора будет выглядеть следующим образом:

Мы видим, что при Т=1с, ошибка I1=![]() =0.210 , Туст=10с

=0.210 , Туст=10с

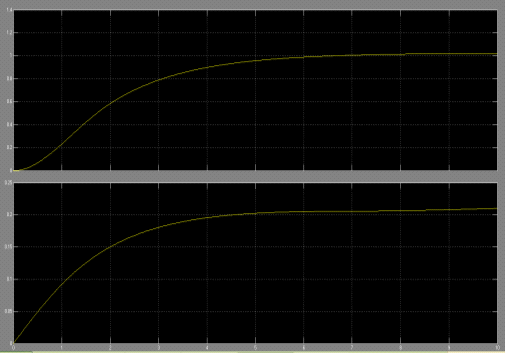

Графики будут следующие:

Минимизируем ошибку I2=![]()

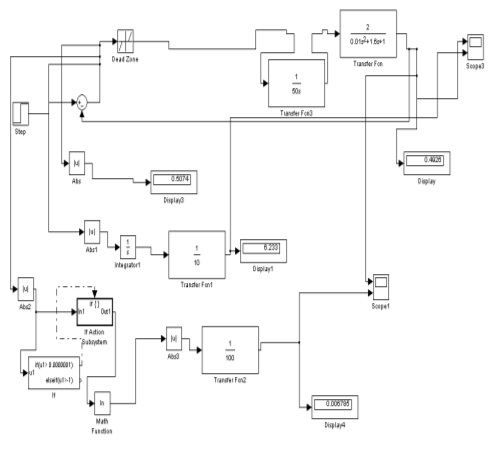

Схема будет следующей:

Мы видим, что при Т=50с, I2=![]() , Туст=100с

, Туст=100с

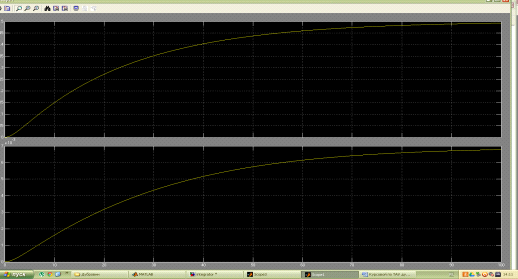

Графики будут следующие:

Статья в тему

Системы связи с подвижными объектами

Рассматривается прямолинейный диспетчерский участок железнодорожной магистрали (рис 1)

Рисунок 1. Диспетчерский участок

Использованные следующие аббревиатуры: ТВЛ - два провода трехфазной высоковольтной линии, ВЛС - воздушная линия связи, ДВ и ОВ - соответственно двух- и однопроводной волноводы. ...