Синхронные триггеры, построенные по принципу двухступенчатого запоминания информации

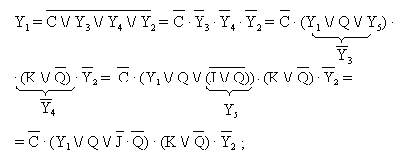

Уровни Y1 и Y2 здесь определяются следующими выражениями:

( (18)

( (18)

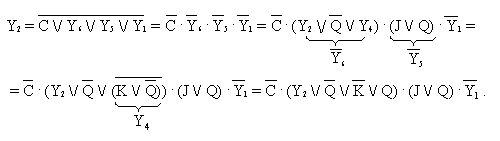

( (19)

( (19)

При С = 1, Y1 = 0, Y2 = 0.

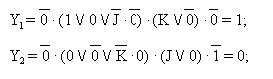

Подставляя значения Y1 = Y2 = 0 в выражения ( 18) и ( 19), получаем для момента отрицательного фронта сигнала на входе С:

![]() ( (20)

( (20)

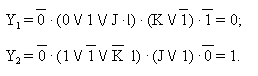

![]() ( (21)

( (21)

Пользуясь этими выражениями, можно построить таблицу состояний триггера после действия фронта сигнала на входе С, (табл. 4). Отсюда следует, что функционирование триггера подчинено таблице переходов JK-триггера (табл. 2.б).

Из табл. 4 видно, что значения Y1, Y2, Q встречаются в двух комбинациях: Y1 = 1; Y2 = 0; Q = 0 и Y1 = 0; Y2 = 1; Q = 1. Если первую из этих комбинаций значений подставить в ( 18) и ( 19), то получим

т.е, комбинация Y1 = 1; Y2 = 0 является устойчивой, и после действия на входе С отрицательного фронта сигнала никакие изменения значений на входах J и К не могут изменить значений управляющих сигналов Y1 и Y2. Следовательно, триггер оказывается нечувствительным к изменению сигналов на входах J и К после действия отрицательного фронта сигнала на входе С.

Подстановка второй комбинации значений Y1, Y2, Q в ( 18) и ( 19) приводит к

Таким образом, и в этом состоянии триггер нечувствителен к изменению сигналов J и К после действия на входе С отрицательного фронта сигнала

Статья в тему

Трасса прокладки ВОЛП между пунктами Екатеринбург-Серов

Научно-технический прогресс во многом определяется скоростью передачи

информации и ее объемом. Возможность резкого увеличения объемов передаваемой

информации наиболее полно реализуется в результате применения

волоконно-оптических линий передачи (ВОЛП), которые по сравнению с такими

ш ...