Синхронные триггеры, построенные по принципу двухступенчатого запоминания информации

Цепи асинхронных входов Rd и Sd показаны на рис. 12,а штриховыми линиями. Условное обозначение D-триггера с асинхронными входами Rd и Sd приведено на рис. 12,в.

На рис. 13 показана схема D-триггера, построенного на элементах ИЛИ-НЕ.

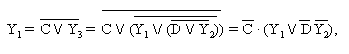

Выражения для логических уровней в точках Y1 и Y2 данной схемы имеют следующий вид (без учета входов Rd и Sd):

( 8)

( 8)

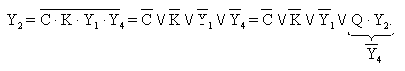

![]() ( 9)

( 9)

Анализ выражений, подобный приведенному выше применительно к триггеру, построенному на элементах И-НЕ, показывает, что переключение триггера происходит при отрицательном фронте сигнала на входе С. При этом переключающие уровни определяются выражениями Y1 = ![]() и Y2=D.

и Y2=D.

На рис. 13,б показано условное обозначение данного триггера.

T-триггер

Рассмотрим работу триггера, схема которого приведена на рис. 14,а.

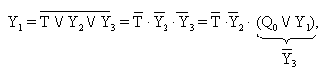

Логические выражения для уровней на управляющих входах Y1 и Y2 (построенные без учета показанных штриховой линией цепей установочных входов Rd и Sd):

(10)

(10)

(11)

(11)

При T = l, Y1 = Y2 = 0 входная триггерная структура сохраняет ранее установленное о ней состояние.

![]()

Найдем для Y1 и Y2 выражения, соответствующие действию на входе Т отрицательного фронта сигнала. Подставив в правые части выражений ( 10) и ( 11) значения Y1 = Y2= 0, получим

Итак, при Q0 = 0 У2 = l и этим уровнем выходная триггерная структура переключается в состояние Q = l; при Q0 = l Y1 = 1, этим уровнем выходная триггерная структура переводится в состояние 0. Таким образом, при действии отрицательного фронта сигнала на входе Т-триггер переключается в состояние Q, противоположное состоянию Q0, в котором он ранее находился. Такое функционирование соответствует таблице состояний Т-триггера (табл. 2,г).

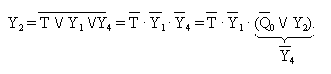

Рассмотрим функционирование триггера со стороны установочных входов Rd и Sd. С учетом этих входов логические выражения для Y1 и Y2 имеют следующий вид:

![]() ( (12)

( (12)

![]() (13)

(13)

![]()

Для установки триггера в состояние Q = 0 подается сигнал Rd = l. При этом из ( 13) Y2 = 0; из ( 12) при T = 0

Под действием таких управляющих сигналов Y1 и Y2 триггер устанавливается в состояние Q = 0. Заметим, что после того, как будет снят сигнал со входа Rd, остаются неизменными уровни Y1 и Y2 и они поддерживают установленное в триггере состояние. Процессы при установке триггера в состояние 1 сигналом на входе Sd анализируются аналогично.

JK-триггep

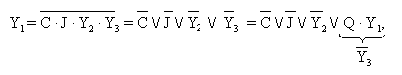

Проанализируем работу триггера, схема которого приведена на рис. 15. Логические выражения для уровней на управляющих входах Y1 и Y2:

( (14)

( (14)

( (15)

( (15)

При C = Q на управляющих входах устанавливаются пассивные уровни Y1 = 1 и Y2 = 1, не влияющие на состояние выходной триггерной структуры. При положительном фронте сигнала на входе С уровни Y1 и Y2 определяются выражениями, получаемыми из ( 14) и ( 15) при подстановке С = 1, Y1 = 1, Y2 = 1:

триггер синхронный моделирование инверсный

![]() ( 16)

( 16)

![]() ( 17)

( 17)

В табл. 3 приведены комбинации входных сигналов J, К и текущего состояния триггера Q0, действующих в момент, непосредственно предшествующей моменту поступления положительного фронта на вход С, а также значения Y1, Y2 и состояния триггера Q для ближайшего момента после фронта сигнала на входе С. Как видно из таблицы, действие сигналов J и К на состояние триггера соответствует таблице состояний JK-триггера (табл. 2б).

Статья в тему

Оценка качества обслуживания промышленного здания

промышленный здание нечеткий множество

Данная курсовая работа строится на основе теории нечетких множеств. С

помощью этой теории и экспертных оценок, мы выявим общую оценку качества

обслуживания промышленного здания.

Для теории нечетких множеств основополагающим понятием являетс ...