Блок-схема цифрового узла

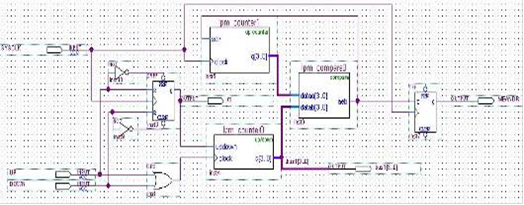

В ходе выполнения лабораторной работы №2 в среде разработки Quartus была разработана блок-схема цифрового узла (Рис. 1), реализующая генератор прямоугольных импульсов с изменяемой частотой (меандр, изменение осуществляется с помощью двух кнопок: «больше», «меньше»).

Рисунок 1 «Блок-схема цифрового узла»

В данной схеме используются следующие компоненты:

1. INPUT - входной порт:

1.1. sysclk - вход тактового генератора;

1.2. up - сигнал кнопки, увеличивающей значение счетчика;

1.3. down - сигнал кнопки, уменьшающей значение счетчика;

2. OUTPUT - выходной порт:

2.1. bus[3 0] - содержимое реверсивного счетчика нажатий кнопок, выведена для диагностики работы схемы;

2.2. RS - состояние RS-триггера, определяющее направление счета в реверсивном счетчике.

2.3. MEANDR - на этот выход подаются прямоугольные импульсы с выбранной частотой.

3. OR2 - логическое ИЛИ.

4. NOT -Инверсия сигнала.

5. RSFF - RS-триггер, задающий направление счета.

6. TFF - T-триггер, формирующий прямоугольные импульсы.

7. Lpm_counter1 - счетчик, созданный путем выбора параметров макрофункции lpm_counter. Настроены следующие параметры: разрядность 4 бита, вход синхронного сброса, вход синхросигнала.

8. Lpm_counter2 - реверсивный счетчик, созданный путем выбора параметров макрофункции lpm_counter. Настроены следующие параметры: разрядность 4 бита, вход направления счета, вход синхросигнала.

9. Lpm_compare - комапратор, созданный путем выбора параметров макрофункции lpm_compare. Настроены следующие параметры: разрядность операндов A и B 4 бита, выход сигнала равенства операндов AeB.

Тестирование работы цифрового узла, описанного блок-схемой, выполнено следующим образом:

1. Необходимо создать файл векторной диаграммы (vector waveform file). Затем в поле Name нужно вставить входные и выходные порты схемы. (Рис. 2)

Рисунок 2 «Добавление портов на диаграмму»

2. Задать входным портам соответствующие значения (рис.3).

Рисунок 3 «Задание значений входных портов»

3. Затем запустить симуляцию.

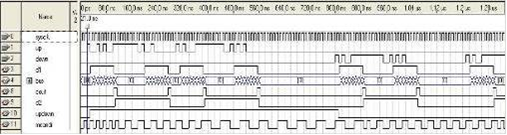

4. Проанализировать полученные результаты (Рис. 4).

Рисунок 4 «Результат симуляции».

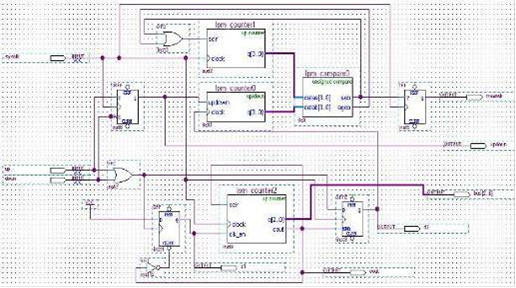

В результате анализа временных диаграмм видно, что при нажатии на кнопку «UP» значение счетчика увеличивается, а частота уменьшается. При нажатии на кнопку «DOWN» значение счетчика уменьшается, а частота увеличивается. Для оптимизации схемы к работе на плате был добавлен счетчик, понижающий частоту мерцания светодиода с 25 МГц до 3 Гц. Также была добавлена цепь подавления дребезга контактов (рис. 5).

Рисунок 5 «Схема с подавлением дребезга»

Рисунок 6 «Подавление дребезга на временной диаграмме».

Статья в тему

Метрологические характеристики АЦП

Цель

работы: экспериментальное определение метрологических

характеристик АЦП, сравнение экспериментальных характеристик АЦП с паспортными

данными и методическими погрешностями АЦП с помощью NI

ELVIS и LabVIEW.

Задание:

. Ознакомится

с имеющейся на рабочем месте аппаратуро ...