Разработка принципиальной схемы основного узла АС БПФ

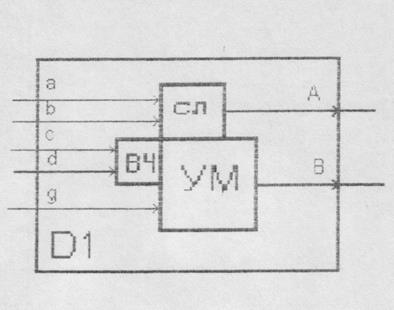

Для основного узла доплеровской РЛСАС БПФ применим основной микропроцессор К1815ВФ3. Структурная схема этого МП приведена на рис 7. Эта микросхема выполняет унифицированную совокупность операций, на основе которой может быть построена каждая из крупных операций ЦОС. На рис 7: Сл - блок операций сложения; Вч - блок операций вычитания; Ум - блок операций умножения; a, b, c, d, g - входы; А и В - выходы.

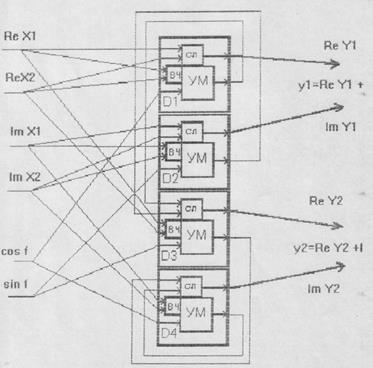

При использовании данного МП для построения процессоров БПФ, необходимо учесть следующее. Выходная информация получается в результате выполнения различных операций (см. рис. 7), так, А = ab; B = (cd)g - это приводит к тому, что если операнды на выход МП поступают синхронно, то результаты на выходе будут появляться асинхронно, как это представлено на обобщенной временной диаграмме рис 8. - т.е. число Ф имеет один масштаб, а В - другой. На рис 9 представлена структурная схема реализации операции БПФ на МП К1815ВФ3. Для реализации БПФ на данной схеме числа на выходе МП должны быть в одном масштабе. Если упрощенно принять, что сумматор и множительное устройство имеют одинаковую задержку, равную D, то с учетом вышеизложенного, МП должен выполнять следующие операции:

1. A = D(ab)B = 2D(cd)g

. A = 2D(ab)B = 2D(cd)g

. A = 3D(ab)B = 2D(cd)g

Здесь символы D; 2D; 3D перед операцией означают, что результат данной операции базируется с задержкой на D, 2D и 3D таков соответственно по отношению к поступающим операндам.

Для этого в блок суммирования вводят управляемую задержку, настраивающуюся с помощью кодов операций. Краткая техническая характеристика БИС и назначение выводов приведены в приложении 3 [4].

Рассмотрим структурную схему реализации БПФ на МП К1815ВФ3 - рис. 9. Из нее видно, что для получения базовой бабочки БПФ требуется 4 МП. Т.о. при N = 8 получим:

МП = N/2/24 = 16 микросхема.

В приложении 4 приведена схема электрическая принципиальная одного из блоков АС БПФ, выполненного на 4-х процессорах К1815 ВФ3, выполняющего базовую «бабочку» БПФ для двух чисел. Для реализации 8-точечного БПФ (N=8) потребуется 4-ре таких блока [4].

Т.о. для заданного N = 8 потребуется:

- МП К1815ВФ3 - 16 шт;

- Резисторов питания-16 шт;

Разъемов 4pin;

Мощность источника питания: 300мА А

Рис. 7. Структурная схема БИС К1815ВФ3

Рис. 8. Временные диаграммы БИС К1815ВФ3

Рис. 9. Структурная схема алгоритма БПФ на К1815ВФ

Статья в тему

Оптико-акустические газоанализаторы

ГАЗОАНАЛИЗАТОРЫ

это приборы, измеряющие содержание (концентрацию) одного или нескольких

компонентов в газовых смесях. Каждый газоанализатор предназначен для измерения

концентрации только определенных компонентов на фоне конкретной газовой смеси в

нормированных условиях. Наряду с испо ...