Расчёты быстродействия

Цель расчета:

Определение максимальной частоты срабатывания схемы.

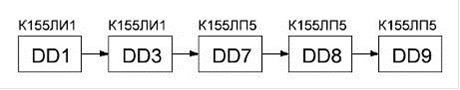

Для определения времени задержки необходимо использовать самую длинную цепочку в схеме, формирующую выходной сигнал.

Исходными данными являются:

1. Схема электрическая принципиальная;

2. Справочник по интегральным микросхемам.

τ∑ = 27+27+30*3=144 н.с

Период повторения подчиняется соотношению: T>> τ∑

f=1/T=1/140*10-9= 7,15 МГц

Результат расчета быстродействия согласуется с техническими требованиями на схеме.

Статья в тему

Графоаналитический расчет звукоизоляции ограждающих конструкций помещения

звукоизоляция защита информация безопасность

Аттестация объекта информатизации по требованиям безопасности информации

представляет собой комплекс организационно-технических мероприятий, в

результате которых подтверждается, что на аттестационном объекте выполнены

требования по безопасно ...