Разработка схемы декодирующего устройства

В каждом из устройств имеется по два регистра - RG1 и RG2. В регистре RG1 для разделимых кодов число ячеек равно числу информационных элементов k.

Места включения инверторов в схемах для исправления ошибок определяются состоянием регистра RG2 в момент поступления ошибочного элемента на верхний вход выходного сумматора по модулю два.

Для исправления ошибочного разряда на нижний вход этого сумматора должен быть подан сигнал логической единицы. Этим и определяется положение инверторов в схеме при потактовом анализе ее работы и подаче на вход комбинации с заранее известным ошибочным разрядом.

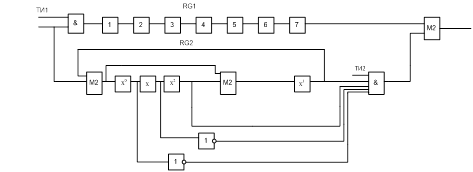

Схема декодирующего устройства приведена на рисунке 6.

Рисунок 6 - Схема декодирующего устройства.

Таблица 4.1 - Потактовая работа схемы декодирующего устройства при приеме правильной комбинации.

|

Такт |

Вход |

RG1 |

RG2 |

ТИ |

Вход выходного сумматора |

Выход |

|

1 |

0 |

0000000 |

0000 |

ТИ1 |

- |

- |

|

2 |

0 |

0000000 |

0000 |

ТИ1 |

- |

- |

|

3 |

0 |

0000000 |

0000 |

ТИ1 |

- |

- |

|

4 |

1 |

1000000 |

1001 |

ТИ1 |

- |

- |

|

5 |

1 |

1100000 |

0100 |

ТИ1 |

- |

- |

|

6 |

1 |

1110000 |

1011 |

ТИ1 |

- |

- |

|

7 |

1 |

1111000 |

0101 |

ТИ1 |

- |

- |

|

8 |

1 |

1111000 |

0010 |

- |

- |

- |

|

9 |

0 |

1111000 |

0001 |

- |

- |

- |

|

10 |

1 |

1111000 |

0000 |

- |

- |

- |

|

11 |

0 |

1111000 |

0000 |

- |

- |

- |

|

12 |

0 |

0111100 |

0000 |

ТИ2 |

0⊕0 |

0 |

|

13 |

0 |

0011110 |

0000 |

ТИ2 |

0⊕0 |

0 |

|

14 |

0 |

0001111 |

0000 |

ТИ2 |

0⊕0 |

0 |

|

15 |

0 |

0000111 |

0000 |

ТИ2 |

0⊕1 |

1 |

|

16 |

0 |

0000011 |

0000 |

ТИ2 |

0⊕1 |

1 |

|

17 |

0 |

0000001 |

0000 |

ТИ2 |

0⊕1 |

1 |

|

18 |

0 |

0000000 |

0000 |

ТИ2 |

0⊕1 |

1 |

Статья в тему

Металлобумажные конденсаторы

конденсатор напряжение электрический диэлектрика

Изобретение электрического конденсатора относится к середине 18 века, но

начало развития конденсаторостроения следует отнести только к самому концу 19

века, когда после изобретения радио А.С. Поповым возникла большая потребность в

конден ...